SOPパッケージにおける小型化設計、プロセス最適化と消費電子への応用

SOP(Small Outline Package:小外形パッケージ)は、従来のDIPを発展させた表面実装型パッケージであり、両側に配置されたガルウィング型リードを通じて基板表面に実装されます。小型化高密度化高周波特性の優位性を持つSOPは、スマートフォン、タブレット、ウェアラブルデバイスなどの消費電子機器に広く採用されています。今日の市場では「軽薄化」「高周波化」が大きな潮流であり、SOPパッケージもその要求に応えるために設計の小型化と製造プロセスの最適化が求められています。

SOPパッケージの小型化設計と構造上の工夫

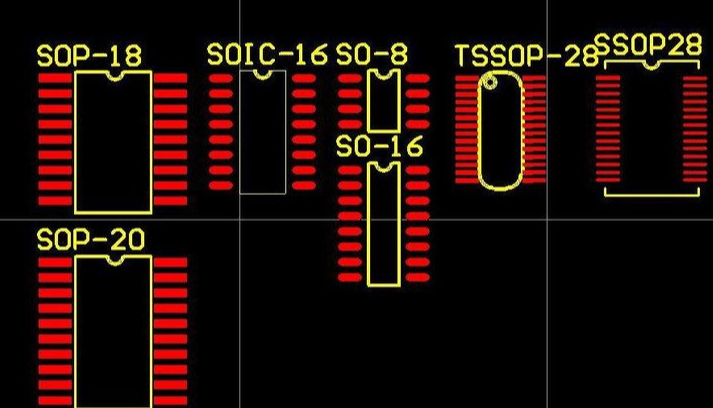

SOPの最大の特長はコンパクトさにあります。パッケージサイズは長さ3-10mm、幅2-6mm、厚さ0.8-1.5mmで、同等リード数のDIPに比べて体積を60%以上削減可能です。リードピッチはDIPの2.54mmから標準SOPでは1.27mm、SSOPでは0.8mm、TSSOPでは0.5mmにまで縮小され、高密度配線を要求する消費電子のPCB設計に最適化されています。リードは外側に湾曲したガルウィング形状を採用しており、基板との接触面積を拡大し、実装信頼性を高めています。

さらに、封止材には耐熱性に優れたエポキシ樹脂を用い、TSSOPなど薄型品では厚さ0.5mmまで対応することで、端末の軽薄化に寄与します。電源管理ICなど高発熱部品向けには、底面に露出パッドを設けた「放熱強化型SOP」が存在し、熱抵抗を大幅に低減しながら安定動作を実現します。

製造プロセスにおける最適化の取り組み

小型化が進むことで実装工程における難易度も上昇するため、SOPでは高度な工法が採用されています。ワイヤーボンディング工程では銅細線(直径18-25μm)を使用し、超音波支援を併用することで強度と安定性を確保します。リード間隔が狭くても短絡を回避できるよう、位置精度やボンディング形状は厳格に管理されます。

実装工程では高精度なビジョン認識付きチップマウンタにより、リードとランドのずれを0.03mm以内に制御。リフロー工程ではSAC305無鉛はんだを用い、240-250℃で安定した接合を実現します。ランド設計は「矩形+延長パッド」とし、立ち上がり不良(いわゆる立ちピン現象)を最小限に抑制します。これらの最適化により、量産においても高い歩留まりが維持されます。

消費電子におけるSOPの適用分野

SOPは小型でありながら高周波信号への適応性が高く、消費電子機器の中核部品に数多く採用されています。スマートフォンでは、RFスイッチやオーディオ処理ICにTSSOPが用いられ、GHz帯域の信号でも低損失伝送が可能です。薄型基板への実装性にも優れ、限られたスペースにおいても高密度実装を可能にしています。

また、ウェアラブルデバイスでは、わずか2×3mm厚さ0.5mmの超小型SOPがセンサーインターフェースICに採用され、省電力設計と合わせて長時間駆動をサポートしています。従来型DIPとの比較では、消費電力を抑制しつつ筐体の薄型化に寄与し、バッテリー寿命の延長に繋がります。

まとめ

SOPパッケージは、その小型化設計と優れた電気的特性により、消費電子業界における主流パッケージとしての地位を確立しています。今後もさらなる軽薄化、高周波対応、高信頼性の基板実装技術が求められる中で、SOPの設計工法の進化は、次世代電子機器の性能向上を支える重要な要素となるでしょう。

--PCBGOGO