高周波信号基板積層の基礎設計原則まとめ

1. 高周波信号がPCB積層に求める基本要件

高周波信号(一般的に10GHz以上。例:5G 28GHz、PCIe 5.0 32Gbps、RF 5GHz)は、積層構造の影響を強く受けやすく、伝送損失、反射、クロストークといった問題が発生しやすくなります。これらの信号に対するPCB積層の基本要件は以下の3点に集約されます。

低伝送損失:高周波では誘電体損失(Df)と導体損失の割合が大きいため、積層設計により全体損失を抑える必要があります。たとえば28GHzでは、挿入損失ILを10mmあたり0.3dB以下に抑えることが求められます。

安定したインピーダンス制御:高周波信号はインピーダンス変動に非常に敏感です。±5%のインピーダンス偏差で反射損失RLが-15dBまで悪化するため、積層での協調設計により±3%以内に制御することが重要です。

低電磁干渉(EMI):高周波信号は放射ノイズを発生しやすく、耐干渉性も低いため、積層内のグランドプレーン設計でクロストークを抑制する必要があります。10GHzではNEXTを-30dB以下に抑えることが推奨されます。

業界データによると、不適切な積層設計では10GHz信号の伝送損失が40%増加し、クロストークが50%増加すると報告されています。そのためPCBメーカーは「シグナルインテグリティを最優先」に基づく基礎設計体系を構築することが重要です。

2. 高周波PCB積層の基礎設計原則

(1) 信号層とグランドプレーンのペアリング

高周波信号のリターンパスはグランドに依存します。信号層がグランド層と適切にペアになっていない場合、リターン経路が拡散し、損失や干渉が増加します。

単端信号(RFフィードラインなど)では、必ず1つの信号層に対して1つの完全なグランドプレーンを対応させ、「信号-グランド」のペアを形成します。グランドをまたぐ分割はリターン経路を50%延長し、損失を20%増加させるため避ける必要があります。また、信号層とグランドの間隔はインピーダンス要件に応じて設計し、厚みの偏差を±5%以内に保つ必要があります。

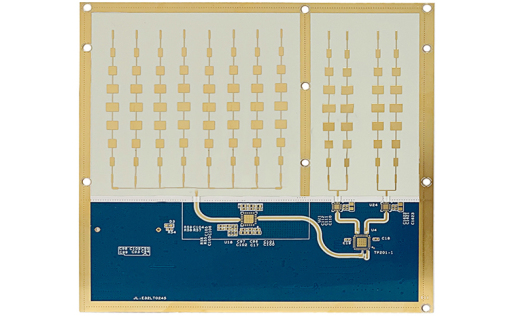

差動信号(PCIe 5.0など)では、信号層をグランドに挟み込む「グランド-信号-グランド」のストリップライン構造が最適です。この構造により、マイクロストリップ構造と比較してクロストークを30%低減し、損失を15%削減できます。一方で、信号層と電源層を直接隣接させると電源ノイズが共通モード干渉を増加させるため、禁止すべき設計となります。

(2) グランドプレーンの完全性

グランドプレーンの分割やスロットは、高周波信号のリターンパスを破壊し、干渉を大幅に増加させます。

高周波領域ではスロットや不要なビアを避け、完全なグランドプレーンを維持します。もし層間接続が必要な場合は、直径0.3mm、ピッチ0.5mm以下のビアアレイを設置し、接続インピーダンスを0.01Ω以下に抑える必要があります。さらに、信号層の外周より0.5mm以上外側にグランドを延長させる「グランド延伸」設計を採用することで、28GHzでの放射損失を15%低減できます。

(3) 誘電体厚みと均一性の制御

高周波信号のインピーダンスは誘電体の厚みに依存するため、厚みの変動がインピーダンス不整合を引き起こします。

マイクロストリップラインでは、介在厚みを0.1?0.2mmに設計し、50Ωや75Ωの目標インピーダンスに合わせます。厚みが0.01mm増加すると、50Ωラインでおよそ2Ωインピーダンスが上昇します。

ストリップラインでは、上下の誘電体厚みを対称にし、偏差を±0.005mm以内に制御します。対称性が崩れると差動インピーダンスの偏差が±4Ω以上となり、信号品質が劣化します。

また、積層後の面内均一性は±3%以内を維持し、たとえば1.6mm基板では局所的な厚み差を0.048mm以下に抑える必要があります。

3. 高周波基板積層におけるインピーダンスマッチングの実現方法

(1) 積層ベースのインピーダンス計算モデル

マイクロストリップラインでは、信号層とグランド層の距離や誘電率に基づきインピーダンスを算出します。たとえばDk=3.8、厚みH=0.15mmの場合、50Ωを実現する線幅は約0.22mmとなります。RFアンテナ給電線や表層の高速信号伝送に適しています。

ストリップラインは上下をグランドで挟んだ構造で、インピーダンス安定性に優れます。温度が±20℃変動してもインピーダンス偏差は±2%以内に収まり、28GHz以上の高周波伝送に適しています。

(2) 積層によるインピーダンス偏差の補償

積層後に誘電体厚みが設計より0.01mm厚い場合、線幅を0.22mmから0.24mmへ調整することで50Ωを維持できます。量産前には試作基板で実測し、「厚み-線幅補償表」を作成することが推奨されます。

また、銅箔の厚みや粗さも影響します。28GHzではスキンデプスが約1.2μmのため、銅箔の粗さRaを0.1μm以下に管理する必要があります。銅箔を35μmから70μmに増加させると50Ωラインで約3Ω低下するため、線幅を0.01mm縮小して補償します。

まとめ

高周波信号PCB積層の設計では、低損失、安定インピーダンス、低EMIを実現するために「信号層とグランド層のペアリング」「グランドプレーンの完全性」「誘電体厚みの制御」が基本原則となります。さらに、インピーダンス計算モデルと補償設計を組み合わせることで、5G、PCIe 5.0、RF通信といった高周波用途に最適な積層を実現できます。