パッド間隔による高速信号のインテグリティ最適化ガイド

基板設計において、高速信号のインテグリティ(信号品質)を確保することは非常に重要です。特に近年のデバイスはより高速かつコンパクト化が進んでおり、信号品質の維持が求められます。その中で見落とされがちな要素の一つが、パッド間隔です。適切なパッド間隔は、クロストークの低減、インピーダンス制御、そして高速回路における信頼性の高いデータ伝送に直結します。本ガイドでは、基板の信号インテグリティにおけるパッド間隔の重要性を解説し、高速設計ルールやクロストーク最小化、差動ペア配線のポイントについて詳しく説明します。

高速基板設計におけるパッド間隔の重要性

高速基板設計では、信号が正確かつ歪みなく伝達されることが求められます。パッド間隔とは、基板上の導電パッド同士の距離を指し、この距離は信号挙動に直接影響を与えます。パッドが近すぎる場合、不要な電気的結合、いわゆるクロストークが発生し、信号品質を低下させる可能性があります。一方、間隔が広すぎると基板レイアウト効率が低下し、インピーダンス特性にも影響します。

高速設計では、信号周波数が100MHzを超えることもあり、わずかなパッド間隔の違いでも深刻な問題を引き起こす場合があります。例えば、パッド間隔が適切でない場合、50Ωや100Ω(差動ペアの場合)のインピーダンスがずれ、反射やデータエラーの原因となります。そのため、パッド間隔は高速信号インテグリティの基礎的かつ重要な要素です。

高速設計における信号インテグリティの基礎

信号インテグリティとは、基板上での電気信号の品質を指します。USB、HDMI、Ethernetなどの高速インターフェースでは、信号インテグリティの維持が安定動作の鍵です。インピーダンスの不整合、クロストーク、信号遅延などがデータ伝送を妨げる要因となります。パッド間隔は、隣接パッドや配線間で発生する電磁干渉(EMI)の程度に影響を与え、これらの要因に直接関わります。

パッド間隔がインピーダンスに与える影響

インピーダンス制御は、高速基板設計の基本原則です。適切なインピーダンスは、信号が配線を沿って伝播する際に反射を防ぎ、データの歪みを抑えます。パッド間隔が狭すぎると、電気容量が増加し、インピーダンスが低下します。特に1GHz以上の高速回路では、インピーダンスのわずかな変動でも信号反射の原因となります。

例えば、典型的な50Ωのシングルエンド配線で、パッド間隔が推奨値以下(細ピッチ部品では約0.2mm)になると、インピーダンスが45Ω以下に低下し、信号損失を引き起こす可能性があります。これを避けるため、基板材料の誘電率(FR-4では一般的に4.2)や目標インピーダンスに基づいた間隔設計が重要です。また、製造前にシミュレーションで影響を確認することも、再設計コストの削減につながります。

インピーダンス制御の実践的なポイント

* 高速部品では、メーカーの最小パッド間隔ガイドライン(通常0.15?0.3mm)を遵守する。

* 内層厚さを均一に保つ(例:0.1?0.2mm)ことでインピーダンスを安定化する。

* 重要信号配線は連続したグラウンドプレーン上で配線し、パッド近接によるインピーダンス変動を抑制する。

クロストーク最小化におけるパッド間隔の役割

クロストークは、高速信号間での不要なエネルギー伝達であり、高速設計での大きな課題です。パッドが近すぎると、周囲の電磁界が結合し干渉が発生します。特に高速信号が並行して走る密集レイアウトでは影響が顕著です。

例えば、パッド間隔が0.1mm未満の場合、USB3.0(5Gbps)のデータ伝送に影響する可能性があります。対策として、パッド間隔を配線幅の3倍以上に設定する、あるいはパッド間にグラウンドビアを配置してシールドする方法があります。これにより、不要な電磁エネルギーを吸収し干渉を低減できます。

クロストーク低減の具体策

* 高速信号では、パッド間隔を最低0.2mm確保する。

* 高速信号パッド間に戦略的にグラウンドパッドやビアを配置する。

* 高速配線はパッド近くで長距離平行配線を避け、交差させて結合を減らす。

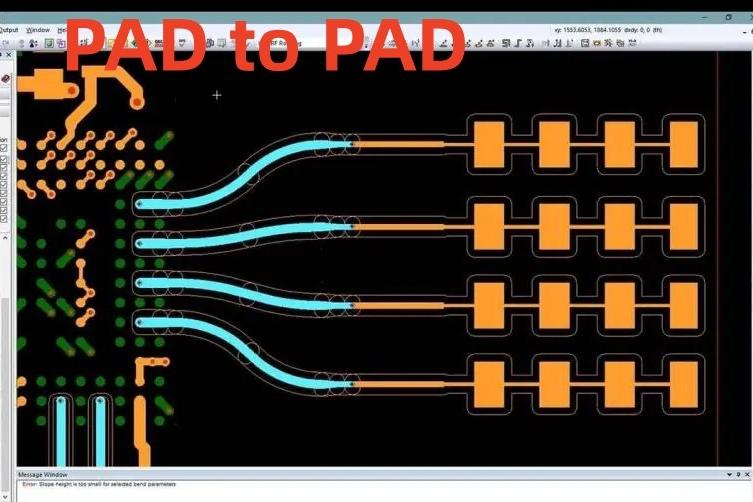

差動ペア配線におけるパッド間隔の注意点

差動ペア配線は、高速設計でノイズを抑えつつデータを伝送する一般的な手法です。USB、Ethernet、PCIeなどで用いられ、2本の信号線が等しく逆位相で動作します。受信側は差分を読み取り、共通モードノイズを打ち消します。

しかし、差動ペアのパッド間隔が不均一、または他信号に近すぎると、信号スキュー(片方の信号が先に到達する現象)が発生します。10ピコ秒の偏差でも、10Gbps信号ではエラーの原因となります。差動ペアのパッド間隔は、対称かつ配線間隔と一致させる必要があります(100Ω差動ペアでは約0.1?0.15mm)。さらに、他高速信号から離すことでクロストークを防ぎます。

差動ペアパッド間隔のベストプラクティス

* パッド間隔を等しく保ち、信号バランスを維持する。

* 他信号パッドから最低0.3mm離す。

* パッド下に連続グラウンド層を配置してインピーダンスを安定化しEMIを低減する。

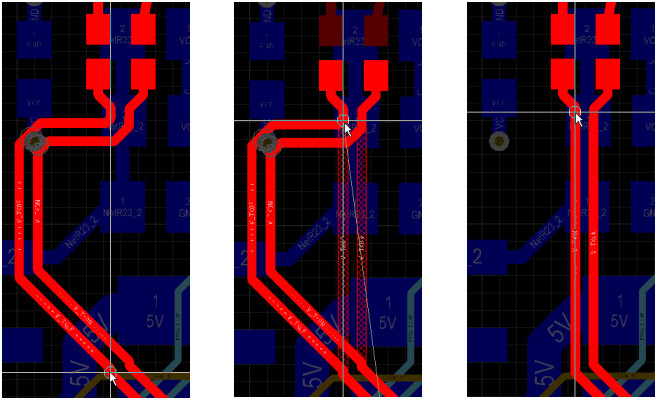

高速設計ルール:パッド間隔とレイアウトのバランス

パッド間隔の最適化は重要ですが、基板全体のレイアウト制約とのバランスが必要です。密集した部品配置では、広い間隔を確保する余地が限られます。この場合、重要信号(クロック線やデータバスなど)に優先して間隔を割り当て、非重要部分はシールド技術で補います。

例えば、1.6mm厚の多層基板では、トップ層の高速信号パッドに0.25mm、内層の低速信号パッドに0.15mmを割り当てることが可能です。基板設計ソフトのDRC(Design Rule Check)を活用することで、製造前に間隔違反を検出し、IPC-2221などの業界基準に適合させることができます。

高速設計パッド間隔の基本ルール

* 信号速度に応じた最小間隔を遵守する。1GHz以上では0.2mm以上が推奨。

* 高速信号パッドは、電源やグラウンドパッドから離すことでノイズ結合を防ぐ。

* シミュレーションでパッド周囲の電磁界を分析し、適切に間隔を調整する。

パッド間隔の課題と解決策

高速信号設計では、パッド間隔と基板サイズのトレードオフが生じます。間隔を広げてクロストークを減らすと、基板サイズが大きくなる場合があります。低誘電率材料(εr<3.5)を使用すると、電容量を減らしつつ間隔を狭められ、信号品質を維持可能です。

BGAなどの細ピッチ部品では、パッド間隔が0.4mm以下になることもあります。この場合、微細ビアやHDI技術を使うことで信号を混雑領域から逃がし、品質を確保できます。

パッド間隔最適化のツールと技術

現代の基板設計ソフトには、阻抗計算、信号インテグリティシミュレーション、自動間隔チェックなどの機能があり、設計段階で問題を予測 - 解決できます。事前シミュレーションで0.15mmパッド間隔が2.5GHz時に過度のクロストークを引き起こすかを確認し、早期に修正可能です。

また、基板製造パートナーと連携することで、実現可能な最小間隔に関する実践的なアドバイスを得られます。高度な工法を持つメーカーでは0.1mmまで対応可能な場合もあれば、安定生産には0.2mm以上が必要な場合もあります。

まとめ:卓越した信号インテグリティのために

パッド間隔は、高速信号インテグリティを実現する上で小さくとも強力な要素です。適切な間隔を設定することで、インピーダンス不整合、クロストーク、信号スキューなどを低減し、高速回路でも信頼性の高い性能を確保できます。差動ペア配線、クロストーク最小化、高速設計ルールの遵守において、パッド間隔の理解は成功の鍵となります。