PCB配線の長さが長すぎると起こる問題とその対策

PCB設計において、配線の長さは信号の完全性や回路性能に大きく影響する重要な要素です。特に高速 - 高周波回路においては、わずかな配線長の違いが大きな機能不良を引き起こすことがあります。配線の長さを適切にコントロールすることは、安定した動作を実現するための基本設計原則と言えます。

undefined配線が長すぎることによる信号遅延とクロストークの問題

配線が必要以上に長くなると、信号伝達に遅延が生じ、隣接配線との電磁結合によってクロストークが発生しやすくなります。特に高速信号では、配線の長さがタイミングマージンを超えることでデータ伝送エラーを引き起こし、機器の信頼性を著しく損なう可能性があります。

例えば、1GHzの高速信号では、10cmの配線で約0.5nsの遅延が発生します。チップのタイミング制約が0.3nsの場合、この遅延は致命的となり、信号が正しくサンプリングされない恐れがあります。また、長い配線は「アンテナ効果」を生み、EMI(電磁妨害)が増大し、隣接信号線への干渉が深刻化します。これにより信号のS/N比が低下し、誤動作やデータ損失の原因となります。

配線長による問題の物理的メカニズム

配線が長くなることで起こる問題は、主に以下の3つの物理的要因によって説明できます。

伝搬遅延の増加

信号の伝搬速度は基板の絶縁体(誘電体)の比誘電率εrに依存しており、以下の式で求められます:

- 伝搬速度(cm/ns)=30 / √εr

一般的な基材であるFR-4のεrは約4.4であるため、信号は約15cm/nsの速度で伝搬します。したがって、1cmあたり約0.067nsの遅延が生じる計算になります。高速回路では、信号周期の1/10以上の遅延がある場合、信号が伝送線路として振る舞い始め、波形の崩れや誤認識を引き起こします。

信号反射の増加

配線が長くなるほど、インピーダンスの不整合による信号の反射が顕著になります。特に配線の幅の急変、ビア(スルーホール)、急角度の折れ曲がりなどがあると反射が発生し、波形にオーバーシュートやリンギングなどの歪みを引き起こします。50cmを超える配線では複数回の反射が発生し、立ち上がり時間の劣化につながります。

リターンパスの増大とEMIの悪化

信号は必ずグラウンドなどのリターンパスを伴って戻るため、配線が長くなるほどループ面積が拡大します。ループ面積が大きくなると、電磁放射(EMI)が強くなり、外部への影響が大きくなると同時に、外部ノイズに対する耐性も低下します。これが製品のEMC(電磁両立性)試験不合格の要因となることもあります。

配線長を最小限に抑える設計戦略

配線長の問題を回避するためには、以下のような設計段階からの対策が有効です。

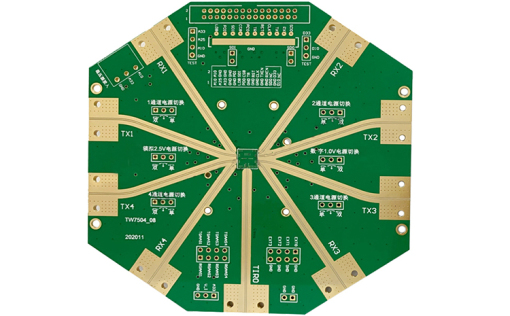

最短距離優先のレイアウト

最も基本的かつ効果的な手法は、関連する部品同士を物理的に近づけて配置し、配線の長さを抑えることです。たとえば、クロックICとそれを受けるマイコンは、できるだけ近接して配置し、クロック線の引き回しを防ぐべきです。

迂回配線の回避

配線経路は「直線優先」で設計し、不要な曲がりや蛇行を避けるようにします。配線長を短縮するためにビアを使って層を切り替えることも有効です。特にPCIeやUSBなどの高速差動信号においては、不必要なルート変更は厳禁です。

パッドからの直接配線

部品のパッドから配線を引き出す際には、できるだけ直線的に目的地に向かうルートを採用し、遠回りを避けます。チップ抵抗などの両端から出る配線は、極力2~3mm程度に抑え、短く直線的に設計することが推奨されます。

BGAやQFPなどの多ピンICでは、ファンアウト配線の長さを2mm以内に制限し、ピン周辺での迷路状配線(スパゲッティ配線)を避ける必要があります。

信号優先度に応じた長さ制御

配線の重要度に応じて、長さの目安を以下のように分類します:

* 最優先 :クロック線、差動信号(DDR、LVDSなど)、リセット線は最も短く(例:10cm以下)保つ必要があります。

* 中程度の優先度 :制御バス(SPI、I2Cなど)は20cm以下を推奨します。

* 低優先度 :GPIOなどの低速信号は30?50cm程度まで許容されますが、高速信号と平行に配線しないように注意します。

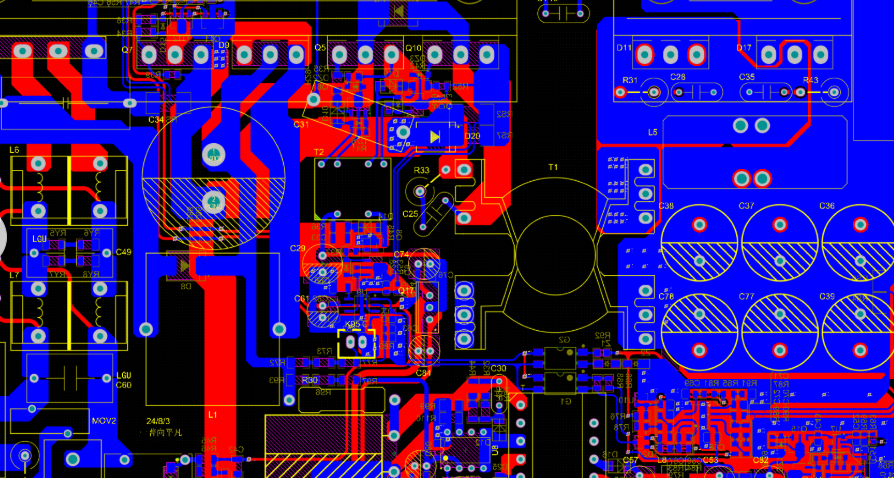

PCB設計ソフトによる長さ管理と警告設定

最新のPCB設計ソフトでは、配線長の監視や制限が可能なDRC(Design Rule Check)機能が搭載されています。

Altium Designerでの設定例

- 配線長ルールの追加- :「Design」→「Rules」→「High Speed」→「Maximum Length」で新規ルールを作成します。

- ネットごとに設定- :クロック用に最大長1000mil(25.4mm)などを設定。DDR用に1500milなど個別に指定可能です。

- リアルタイム警告- :ルール超過時は配線が赤色表示され、警告が「Messages」ウィンドウに表示されます。

KiCadでの設定方法

「PCB Editor」→「Board Setup」→「Design Rules」→「Constraints」から「Net Classes」を開きます。

ネットクラスごとに「Max Length(最大長)」を入力します。

「Run DRC」で配線長のチェックを実行し、違反箇所を特定します。

実例:クロック配線の最適化

あるマイコンシステムにおいて、クロック配線の最適化前後を比較した事例をご紹介します。

* 最適化前 :クロックICとマイコンの距離が15cmで、実際の配線は18cmに及び、電源ラインと平行に配線されていました。信号遅延は約1.2nsで、タイミング要件を超えていました。

* 最適化後 :クロックICをマイコンの近傍(3cm)に再配置し、配線も直線的に3.5cmに短縮。遅延は0.23nsに減少し、両側にグランドビアを配置してクロストークを大幅に抑制しました。

この結果、信号の立ち上がりの歪みが解消され、過渡的な振動も見られなくなりました。EMIも大幅に低減し、規格試験にも余裕をもって合格しました。

設計初期からの配線長管理が成功の鍵

配線長による問題は、設計後半で発覚すると改版コストが高くつくため、設計初期の段階から意識しておくことが重要です。

* レイアウト段階 :信号の流れや機能ブロックに基づき、配置段階で配線長を予測します。

* 配線段階 :重要信号から優先的に配線し、DRCによる長さチェックを活用してリアルタイムで監視します。

* 検証段階 :必要に応じてSI(Signal Integrity)解析を実施し、配線の長さがタイミングに及ぼす影響を確認します。

PCB配線の長さは、ただの寸法ではなく、回路の安定性と信頼性を左右する「隠れた設計パラメータ」です。設計フローのすべての段階で配線長を意識することで、設計ミスによる再設計のリスクを回避し、製品の高品質化につなげることができます。

--PCBGOGO